|

|

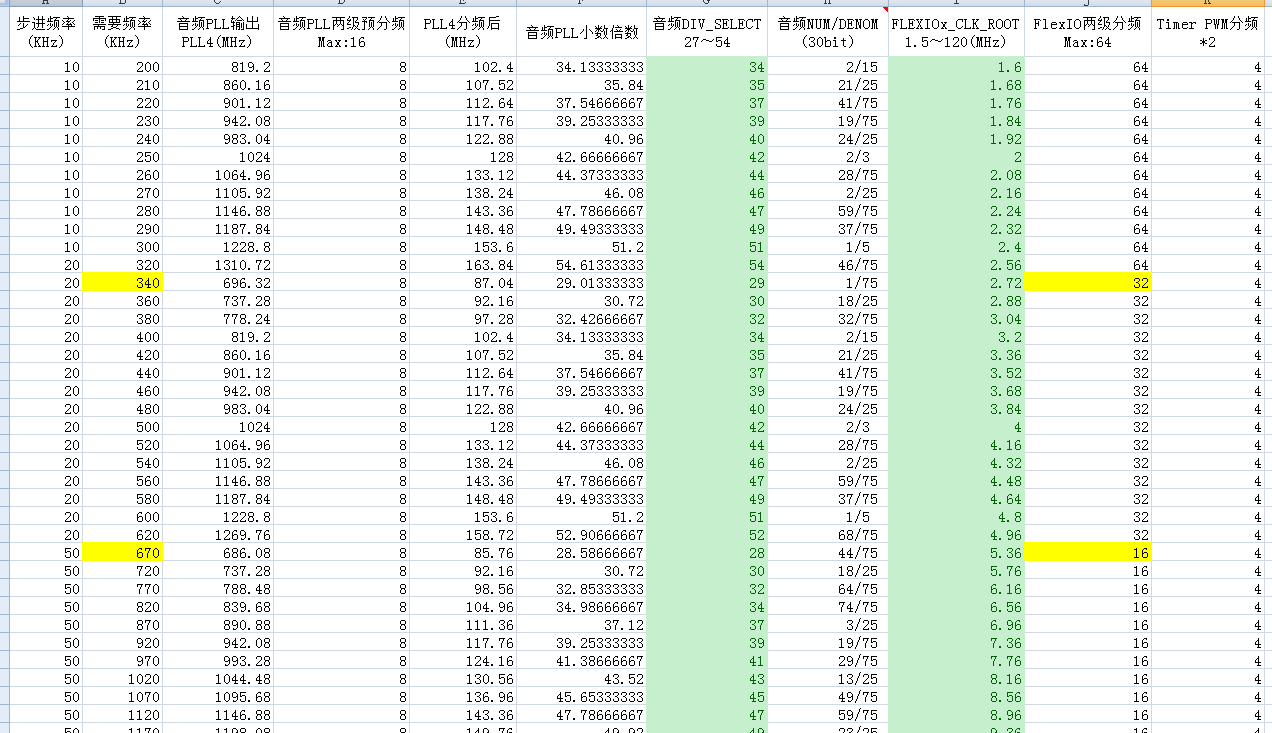

ЮвУЧЕФВњЦЗжавЊЪЙгУвЛИіБШНЯЬиБ№ЕФЦЕТЪЃЌдРДЯыЪЙгУЭтВПЕФ24MHzМгЖЈжЦЦЕТЪЕФгадДеёЕДЦїЃЈДгLVDSЪфШыЃЉЃЌКѓРДВЛЭЃЕФЭкОђЪ§ОнЪжВсЃЌ

ПДЕНRT1052жагаЗжЪ§ЗжЦЕЙІФмЃЌОЋЖШГЌЙ§СЫЮвдРДЕФЯыЯѓЃЌОѕЕУВЛПЩЫМвщЃЌЧыДѓМвПДПДЪЧВЛЪЧетУДЛиЪТЃП

ЪжВсЃК416вГ

PLL4 (also referred to as an Audio PLL) - This is a fractional multiplier PLL used

for generating a low jitter and high precision audio clock with standardized audio

frequencies. The PLLs oscillator frequency range is from 650 MHz to 1300 MHz,

and the frequency resolution is better than 1 Hz....

ЪжВсЃК772вГ

18.8.9 Numerator of Audio PLL Fractional Loop Divider Register

(CCM_ANALOG_PLL_AUDIO_NUM)

This register contains the numerator (A) of Audio PLL fractional loop divider.(Signed number),

absolute value should be less than denominator

Field Description

31ЈC30- Always set to zero (0).

A 30 bit numerator of fractional loop divider.

ЪжВсЃК773вГ

18.8.10 Denominator of Audio PLL Fractional Loop Divider

Register (CCM_ANALOG_PLL_AUDIO_DENOM)

This register contains the Denominator (B) of Audio PLL fractional loop divider.(unsigned number)

Field Description

31ЈC30- Always set to zero (0).

B 30 bit Denominator of fractional loop divider.

ашЧѓЕФЦЕТЪ=480MHz*A/B

Р§ЃК480*99999/100000=479.9952(MHz)

ЧыДѓЯРжИЕМвЛЯТЃЌЪЧетбљТ№ЃП

ЃЈЮвИаЕНКмОЊЦцЃЁЃЉ

|

|

ЗЂБэгк 2018-1-4 14:04:03

ЗЂБэгк 2018-1-4 14:04:03

ТЅжї

ТЅжї

ЧхГўЕФЛяАщжИЬѕЕРЃЁ

ЧхГўЕФЛяАщжИЬѕЕРЃЁ