本帖最后由 spi-sd 于 2025-5-15 00:01 编辑

发个贴问一下,这个ai总结的对吗?

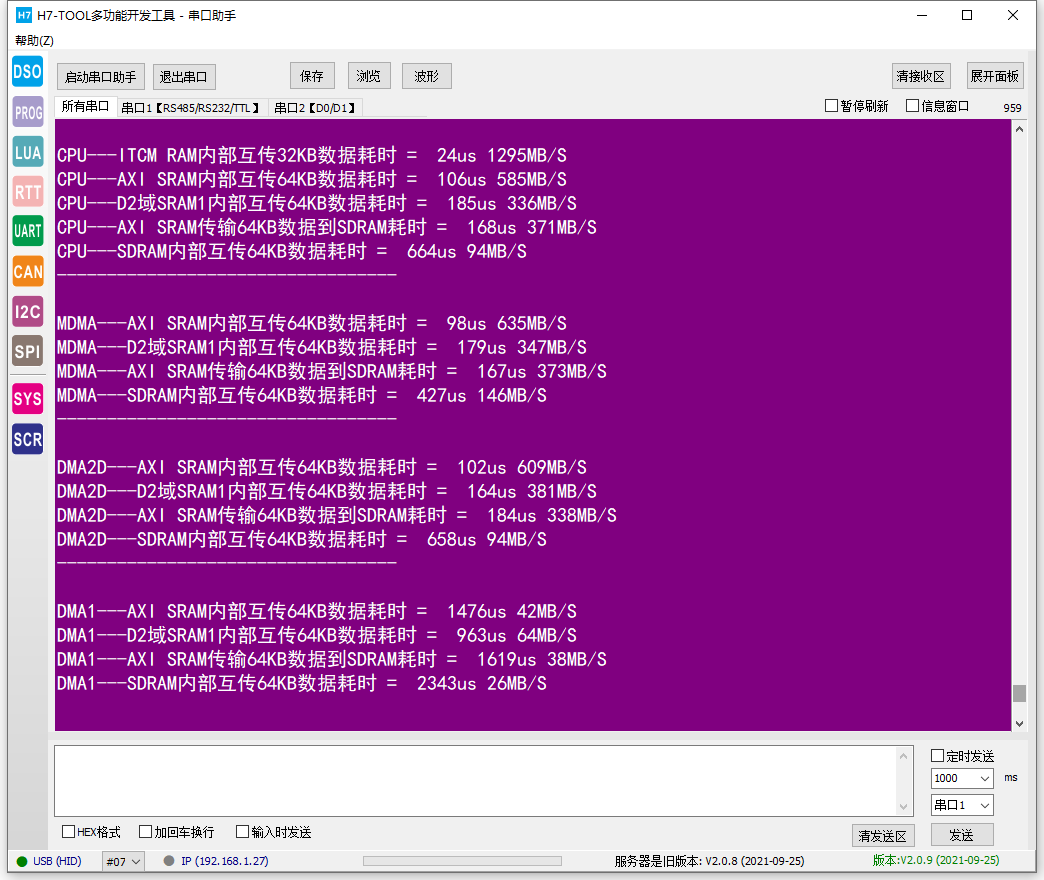

在STM32H750微控制器中,不同SRAM模块的访问速度受其总线架构、时钟频率以及CPU缓存机制的影响。以下是各类SRAM的速度排序及关键特性分析:

1. 最快的RAM:ITCM RAM (64 KB)位置:直接连接至Cortex-M7内核的ITCM接口(指令紧耦合内存)。 速度:零等待周期(与CPU同频,高达480 MHz),访问延迟最低。 用途:存放对延迟极度敏感的代码或数据(需通过特定链接脚本配置)。 限制:仅CPU可直接访问,DMA无法操作。

2. 次快的RAM:DTCM RAM (128 KB)位置:连接至Cortex-M7的DTCM接口(数据紧耦合内存)。 速度:零等待周期(与CPU同频),专为数据操作优化。 用途:高频数据存取(如栈、中断变量),DMA不可访问。 优势:比AXI SRAM快约50%以上(实测约2.5 CPU周期 vs 5+周期)。

3. 三级缓存加速的RAM:AXI SRAM (512 KB) & SRAM1-4 (共1.15 MB)

4. 最慢的RAM:Backup SRAM (4 KB)

关键影响因素缓存配置:启用MPU配置为Write-Through或Write-Back可提升AXI/AHB SRAM的实时性能。 总线竞争:多主设备(如DMA、以太网)同时访问AXI SRAM会引入延迟。 代码优化:将关键数据段放入DTCM(通过__attribute__((section(".dtcm"))))。

速度排序总结

推荐使用场景通过合理配置MPU和链接脚本,可最大化利用STM32H750的高速内存层级。

在STM32H750中,AXI SRAM和SRAM1-4的访问速度排序如下(从最快到最慢):

1. AXI SRAM (512 KB) —— 最快

2. SRAM1 & SRAM2 (各128 KB) —— 次快

3. SRAM3 (32 KB) —— 较慢

4. SRAM4 (64 KB) —— 最慢

速度排序总结AXI SRAM(缓存加速) > SRAM1/SRAM2(AHB总线) > SRAM3 > SRAM4(D3域低速)

关键差异对比[td]SRAM类型 | 总线带宽 | 默认缓存 | 典型延迟(未缓存) | 优化建议 | | AXI SRAM | 64-bit | 是 | 5-6周期 | 优先用于DMA/高频数据 | | SRAM1/SRAM2 | 32-bit | 否 | 6-8周期 | 启用MPU缓存提速 | | SRAM3 | 32-bit | 否 | 7-9周期 | 小数据存储 | | SRAM4 | 32-bit | 否 | 10+周期(D3域限制) | 仅用于低功耗需求场景 |

|

发表于 2025-5-14 23:53:22

发表于 2025-5-14 23:53:22

发表于 2025-5-15 07:08:45

发表于 2025-5-15 07:08:45

楼主

楼主