本帖最后由 Penguins 于 2025-5-2 11:08 编辑

各位大神,笔者为H7新手玩家,移植G4串口+DMA程序时可直接跑通,CubeMX中未使能Cache,未配置MPU,使用通用DMA(未配置MDMA)。

后续在手册发现H7分为D1/2/3 Domain,了解到通用DMA1/2无法访问DTCM区域(0x20000000+128KB),经检查map文件发现确实只使用了AXI SRAM区域(0x24000000+512KB)。

[C] 纯文本查看 复制代码 [b]Execution Region RW_IRAM1 (Exec base: 0x20000000, Load base: 0x08006b50, Size: 0x00000000, Max: 0x00020000, ABSOLUTE)[/b]

[u]**** No section assigned to this execution region ****[/u]

[b]Execution Region RW_IRAM2 (Exec base: 0x24000000, Load base: 0x08006b50, Size: 0x00001268, Max: 0x00080000, ABSOLUTE)[/b]

Exec Addr Load Addr Size Type Attr Idx E Section Name Object

0x24000000 0x08006b50 0x00000008 Data RW 711 .data..L_MergedGlobals stm32h7xx_hal.o

0x24000008 0x08006b58 0x00000008 Data RW 1113 .data..L_MergedGlobals system_stm32h7xx.o

[u]0x24000010 0x08006b60 0x000000d0 Data RW 17 .data.myUART main.o[/u]

0x240000e0 - 0x00000078 Zero RW 57 .bss.hdma_usart1_rx usart.o

0x24000158 - 0x00000078 Zero RW 56 .bss.hdma_usart1_tx usart.o

0x240001d0 - 0x00000094 Zero RW 55 .bss.huart1 usart.o

0x24000264 - 0x00000004 Zero RW 710 .bss.uwTick stm32h7xx_hal.o

0x24000268 - 0x00001000 Zero RW 1 STACK startup_stm32h743xx.o

对此有若干问题:

- 后续计划使用Cache,应当如何决定将何数据分配至DTCM,何数据分配至AXI SRAM及其他SRAM1/2/3/4

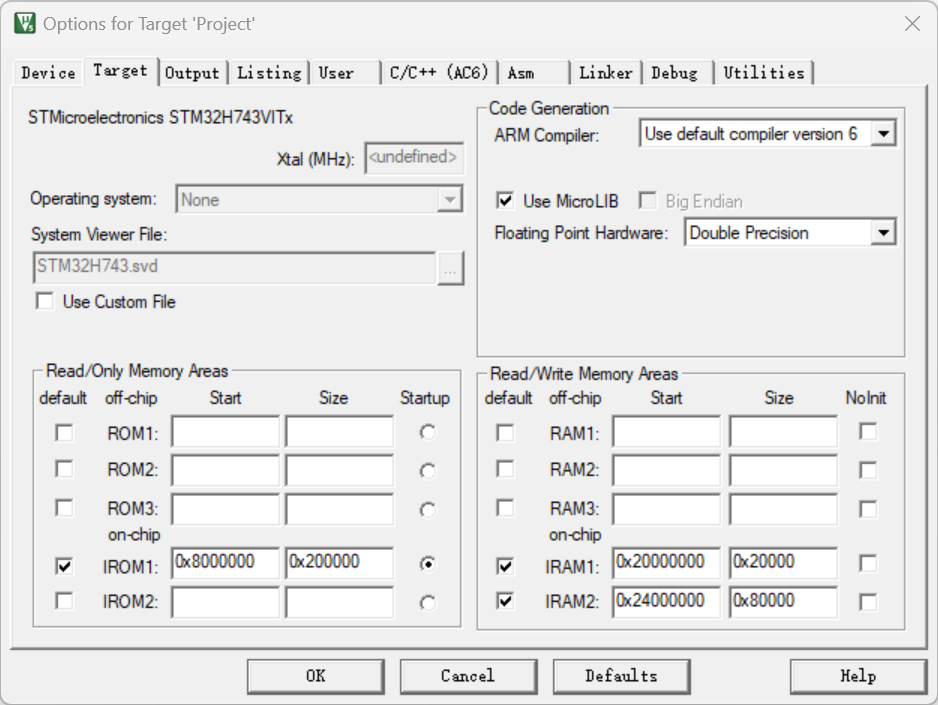

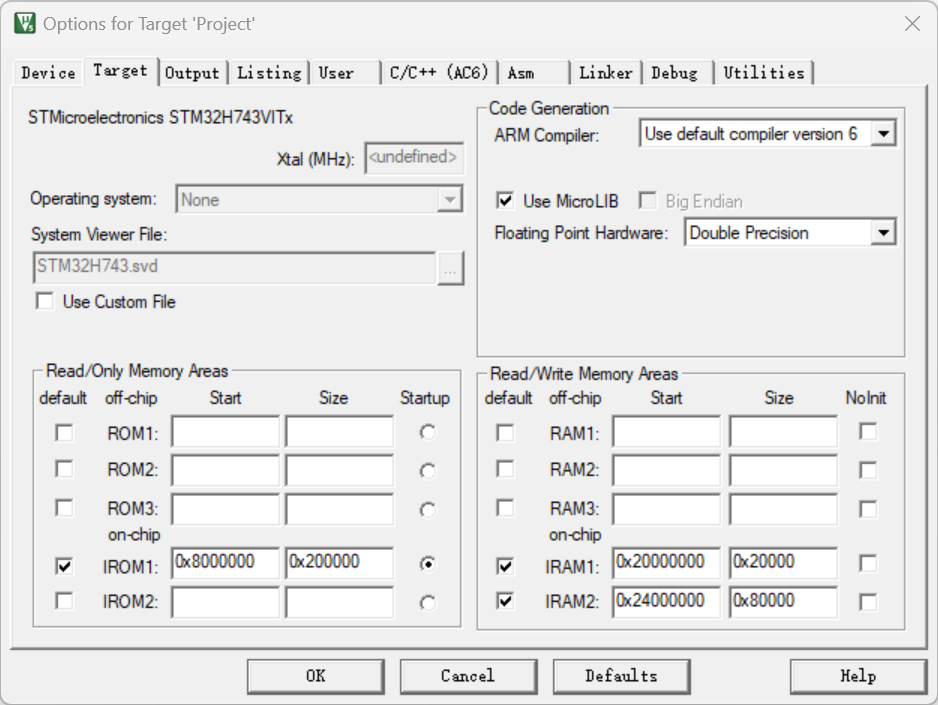

- Keil魔术棒中IRAM仅有2个区域,对应DTCM和AXI SRAM,那么其他SRAM1/2/3/4是如何被使用的

- 对于将被DMA读写的数据,推荐使用mpu禁用此区域cache的方法,还是在dma收发前CleanInvalidate的方法

|

发表于 2025-5-2 11:06:41

发表于 2025-5-2 11:06:41

发表于 2025-5-2 15:36:39

发表于 2025-5-2 15:36:39

楼主

楼主