我看到STM32L431中的C代码中有下面这样的配置:

[C] 纯文本查看 复制代码 #if defined(USART_CR1_FIFOEN)

/**

* @brief Calculate the number of data to process in RX/TX ISR.

* @note The RX FIFO depth and the TX FIFO depth is extracted from

* the UART configuration registers.

* @param huart UART handle.

* @retval None

*/

static void UARTEx_SetNbDataToProcess(UART_HandleTypeDef *huart)

{

uint8_t rx_fifo_depth;

uint8_t tx_fifo_depth;

uint8_t rx_fifo_threshold;

uint8_t tx_fifo_threshold;

static const uint8_t numerator[] = {1U, 1U, 1U, 3U, 7U, 1U, 0U, 0U};

static const uint8_t denominator[] = {8U, 4U, 2U, 4U, 8U, 1U, 1U, 1U};

if (huart->FifoMode == UART_FIFOMODE_DISABLE)

{

huart->NbTxDataToProcess = 1U;

huart->NbRxDataToProcess = 1U;

}

else

{

rx_fifo_depth = RX_FIFO_DEPTH;

tx_fifo_depth = TX_FIFO_DEPTH;

rx_fifo_threshold = (uint8_t)(READ_BIT(huart->Instance->CR3, USART_CR3_RXFTCFG) >> USART_CR3_RXFTCFG_Pos);

tx_fifo_threshold = (uint8_t)(READ_BIT(huart->Instance->CR3, USART_CR3_TXFTCFG) >> USART_CR3_TXFTCFG_Pos);

huart->NbTxDataToProcess = ((uint16_t)tx_fifo_depth * numerator[tx_fifo_threshold]) /

(uint16_t)denominator[tx_fifo_threshold];

huart->NbRxDataToProcess = ((uint16_t)rx_fifo_depth * numerator[rx_fifo_threshold]) /

(uint16_t)denominator[rx_fifo_threshold];

}

}

#endif /* USART_CR1_FIFOEN */

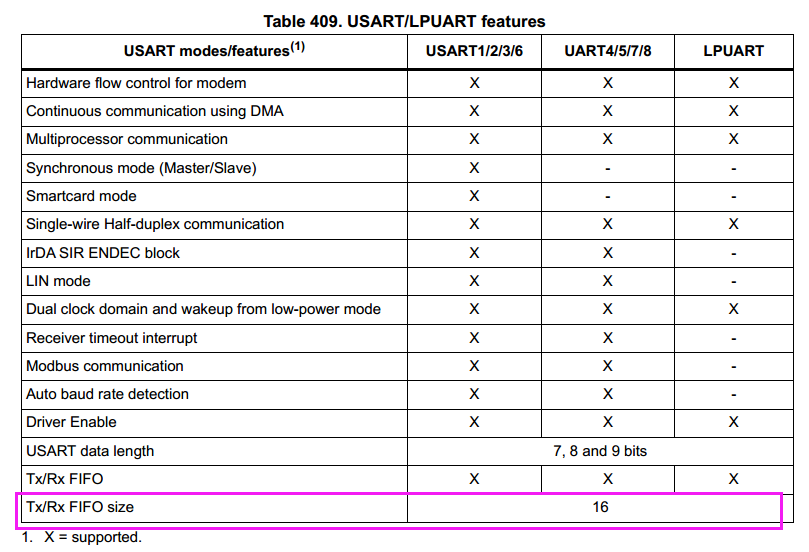

并且可以根据您提供的资料,通过下面资料得到有8个字节的FIFO内容:

[C] 纯文本查看 复制代码 #if defined(USART_CR1_FIFOEN)

/** @defgroup UARTEX_Private_Constants UARTEx Private Constants

* @{

*/

/* UART RX FIFO depth */

#define RX_FIFO_DEPTH 8U

/* UART TX FIFO depth */

#define TX_FIFO_DEPTH 8U

/**

* @}

*/

#endif /* USART_CR1_FIFOEN */

其中看到必须设置宏定义USART_CR1_FIFOEN才能生效,我在问AI的时候,他说只需要配置初始化完成后,在使用普通HAL的API时会自动进行管理。

并且我看到通过CubeMX生成的代码并没有打开USART_CR1_FIFOEN宏定义,应该默认是没有启用,那么请问:

1. 通过CubeMX进行全局启用是可行的吗?或者是通过Keil配置呢?

2. 在上面您回答我的问题中,如果我使用_DMA()方式传输,并且加入DMA也有对应的FIFO通过类似我上面提供的方式打开时,在传输中的硬件流程如下:

先把数据传到DMA的FIFO中,然后由DMA的FIFO传输到UART的FIFO中,依次类推直到传输正式结束。

是否正确? |

发表于 2021-2-27 09:07:25

发表于 2021-2-27 09:07:25

楼主

楼主 发表于 2023-4-12 14:55:26

发表于 2023-4-12 14:55:26