|

|

说明:网上有一个《Verilog的135个经典实例分析》,感觉这个资料非常的不错,自己先潜下心来

把这个135个例子好好学一下。

王金明:《Verilog HDL程序设计教程》

4位加法器- module verilog_prj(cout,sum,ina,inb,cin);

- output[3:0] sum;

- output cout;

- input[3:0] ina,inb;

- input cin;

- assign {cout,sum}=ina+inb+cin;

- endmodule

(1) {} 位拼接运算符

{信号1的某几位,信号2的某几位,..,..,信号n的某几位}

即把某些信号的某些位详细地列出来,中间用逗号分开,最后用大括号括起来表示一个整体信号。见

下例:

{a,b[3:0],w,3 ’ b101}

也可以写成为

{a,b[3],b[2],b[1],b[0],w,1 ’ b1,1’ b0,1’ b1}

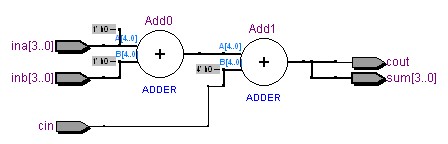

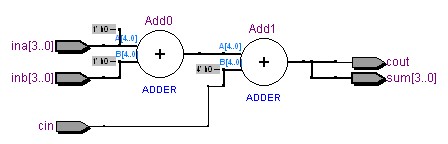

RTL Viewer

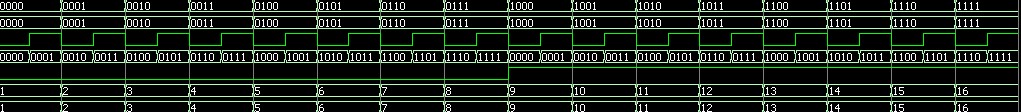

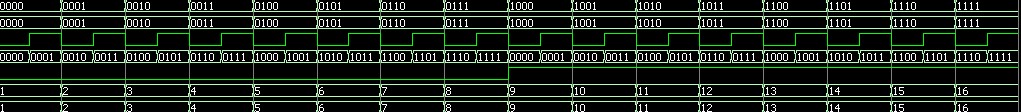

功能仿真(仿真工具ModelSim SE 6.5)

- timescale 1ns/1ns

- module adder_tp; //测试模块的名字

- reg[3:0] a,b; //测试输入信号定义为reg型

- reg cin;

- wire[3:0] sum; //测试输出信号定义为wire型

- wire cout;

- integer i,j;

-

- verilog_prj adder(cout,sum,a,b,cin); //调用测试对象

- always #5 cin=~cin; //设定cin的取值

-

- initial

- begin

- a=0;b=0;cin=0;

- for(i=1;i<16;i=i+1)

- #10 a=i; //设定a的取值

- end

-

- initial

- begin

- for(j=1;j<16;j=j+1)

- #10 b=j; //设定b的取值

- end

-

- initial //定义结果显示格式

- begin

- $monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum);

- #160 $stop;

- end

- endmodule

|

|

发表于 2013-1-14 21:38:05

发表于 2013-1-14 21:38:05

楼主

楼主