最近在用stm32 与w5500做 spi通讯 纪录一下遇到较少见的问题(不专业纪录,有错在麻烦指点 谢谢)

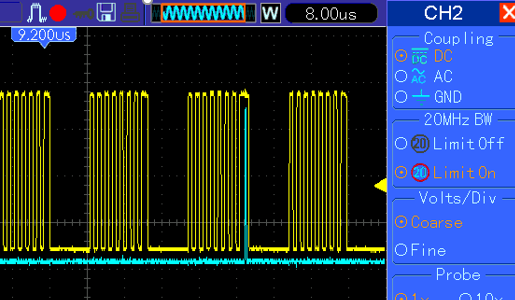

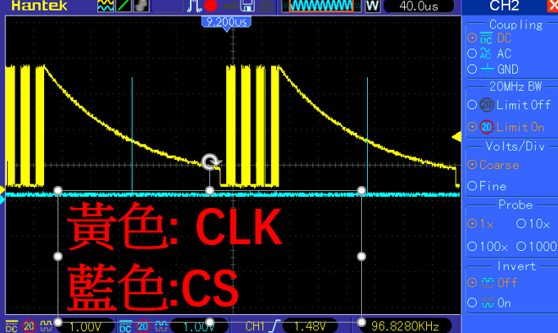

•1 确认cs clk mosi miso 之间的相位(如下图 clk超过cs结束位置),所以要加上延迟

•2 若设定了传输期间关闭中断标志__set_PRIMASK(像是W5500范例代码) 须注意CS信号加上延迟会

因无法产生中断而卡死(我用for loop 延迟)(不知有无更优雅的方法?)

•3 stm32 nucleo 中有些脚位像是H7的B14有接一个板上LED灯, 这时miso信号会不稳(示波器量几乎无讯号)

(这是真的坑,当初拔起来量miso是正常的,但没有插着量就以为没事)

•4 H7的SPI_2 有用到PC2_C PC3_C 脚,这个脚是类比用的,但官方IDE还是可以选(经查询似乎也不是不能用 ?,只是处理起来感觉麻烦了点)

•5 管脚时钟跟SPI时钟要打开(这些IDE默认是会自动配好的,可以不管)

__HAL_RCC_SPIX_CLK_ENABLE(); SPI时钟打开

__HAL_RCC_GPIOX_CLK_ENABLE(); GPIO时钟打开

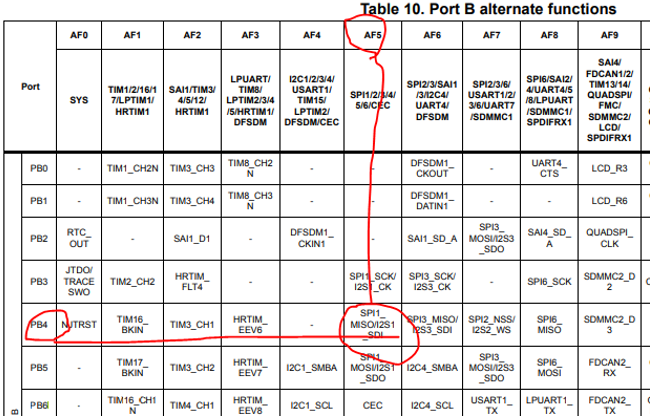

GPIO_InitStruct.Alternate = GPIO_AFX_SPIX; 引脚复用功能(参考手册如下图)(IDE也会自动配)

6 GPIO 管脚速度依需求设置(不能啥都设very high 会翻车)(我低速2M想说怎还无法通讯结果设回LOW就好了)

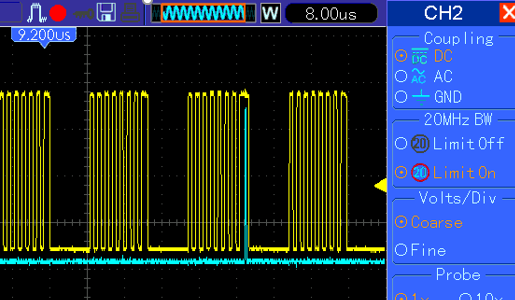

另外有一个奇怪的现象想问一下, SPI CLK没有上拉电阻时CLK是下图这样,但是CS信号左右延迟设大设小这斜波就跟着缩放, 查了一下好像是信号容性有关,可是我是硬件SPI (只有CS是软件控制)照理说CLK这斜波持续时间不是应该固定的吗?怎么会 跟着沿时拉长呢? CLK没上拉时是下面这样 (加了上拉后就是完美的高电平了 忘记截上拉后的图)

|

发表于 2024-8-5 22:43:00

发表于 2024-8-5 22:43:00

发表于 2024-8-7 09:02:19

发表于 2024-8-7 09:02:19